Авторитетность издания

ВАК - К1

RSCI, ядро РИНЦ

Добавить в закладки

Следующий номер на сайте

№2

Ожидается:

16 Июня 2024

Особенности применения объектно-ориентированного проектирования встроенных систем жесткого реального времени

Application features of object-oriented design for hard real time embedded systems

Дата подачи статьи: 25.12.2015

УДК: 004.4’2

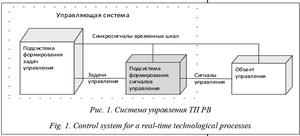

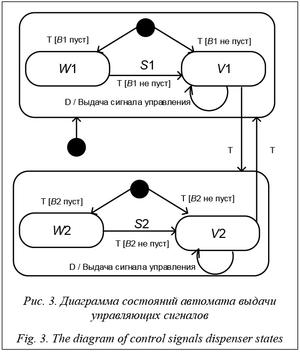

Статья опубликована в выпуске журнала № 1 за 2016 год. [ на стр. 56-59 ]Аннотация:Рассмотрены проблемы, возникающие в процессе объектно-ориентированной разработки функционального ПО встроенных систем реального времени. Сформулированы типы задач, которые требуют реализации на языках программирования и языках описания аппаратуры. Процессорные элементы гетерогенных вычислительных платформ характеризуются значительными объемами основной и внешней памяти, гибкостью реализуемых алгоритмов управления и форматов данных, в то время как элементы ядер, реализованные на языках описания аппаратуры, обеспечивают существенно большее быстродействие. Предложены принципы декомпозиции функционального ПО для реализации на гетерогенной вычислительной платформе, заключающиеся в объединении в подсистемы объектов, имеющих близкие требования к времени реакции на события, соответствующие элементу аппаратной платформы. Описан пример их применения, в качестве которого рассмотрен процесс проектирования элемента системы управления технологическим процессом в реальном времени, имеющим ограничения в виде двух временных шкал. Описаны подсистема, работающая в миллисекундном цикле и программно реализованная в среде операционной системы реального времени, и подсистема микросекундного цикла, реализованная в программируемых логических блоках. Приведены диаграммы декомпозиции и состояний, а также временная диаграмма, описывающая загрузку основных ресурсов аппаратуры. Кроме этого, определены временные ограничения, которым должна удовлетворять программная подсистема. Применение описанных принципов декомпозиции на практике показало, что использование данного подхода позволяет обеспечить рациональное распределение нагрузки на элементы аппаратной платформы и обеспечить выполнение ограничений в работе программно-аппаратной системы, накладываемых требованием обеспечения режима работы жесткого реального времени.

Abstract:The article considers the problems of object-oriented software development of embedded real-time systems. It also discusses the problems that require implementation using programming languages and hardware description languages. A particular feature of processing elements of heterogeneous computing platforms is a significant volume of main and external memory, as well as flexibility of implemented control algorithms and data formats. At the same time, kernel elements implemented in hardware description languages provide greater speed. The paper suggests the principles of a functional software decomposition for the purposes of implementation on a hetero-geneous computing platform. They bring together objects with similar requirements for events response time in subsystems. The events are relevant to an element of a hardware platform. The paper describes an example of their application, which includes an element design process of a real-time technological process control system that have limitations in two time scales. The paper describes the subsystem operating in a millisecond cycle. It is implemented as the software component for a Linux-based RTOS environment. There also is a microsecond cycle subsystem implemented in FPGA. The paper presents a decomposition diagram and a diagram of conditions, as well as a timing chart describing the basic resource loading equipment. In addition, the paper defines the time limit for the software subsystem. As a result, practical application of the described RTES decomposition principles shown that this approach allows a reasonable distribution of loads on a hardware platform and enforces restrictions in hardware and software parts of the system imposed by the requirement of a hard real-time operation mode.

| Авторы: Аржаев В.И. (arzhaeVI@cps.tver.ru) - НИИ «Центрпрограммсистем» (зав. отделением), Тверь, Россия, кандидат технических наук, Скворцов А.В. (skvortsovAV@cps.tver.ru) - НИИ «Центрпрограммсистем» (зав. отделом), Тверь, Россия, кандидат технических наук | |

| Ключевые слова: рсу, распределенная система управления, uml, унифицированный язык визуального моделирования, проектирование и разработка по, распределенные встроенные системы реального времени |

|

| Keywords: dcs, distributed control system, uml, unified modeling language, software design and programming, distributed real-time embedded systems |

|

| Количество просмотров: 5787 |

Версия для печати Выпуск в формате PDF (8.31Мб) Скачать обложку в формате PDF (1.24Мб) |

| Постоянный адрес статьи: http://swsys.ru/index.php?page=article&id=4110&lang= |

Версия для печати Выпуск в формате PDF (8.31Мб) Скачать обложку в формате PDF (1.24Мб) |

| Статья опубликована в выпуске журнала № 1 за 2016 год. [ на стр. 56-59 ] |

Возможно, Вас заинтересуют следующие статьи схожих тематик:

- Генератор текста программ в исходном виде для систем реального времени

- Применение трансформаций таблиц решений при создании интеллектуального программного модуля «Детектор» для веб-приложений

- Проектирование интерпретатора языка QVT Operational Mappings для программного средства UML Refactoring в рамках модельно-ориентированного подхода

- Web-сервис для автоматизированного формирования продукционных баз знаний на основе концептуальных моделей

- Методы сокращения количества уязвимостей в специальном программном обеспечении реального времени

Назад, к списку статей

, где Сф – время выполнения одного цикла задачи формирователя (обработки одного задания); Сп – время выполнения одного цикла задачи планировщика (выдачи аппаратным средствам одной управляющей последовательности); Т – период синхросигнала шкалы Т.

, где Сф – время выполнения одного цикла задачи формирователя (обработки одного задания); Сп – время выполнения одного цикла задачи планировщика (выдачи аппаратным средствам одной управляющей последовательности); Т – период синхросигнала шкалы Т.