Любая многопроцессорная система должна быть проинициализирована по включении питания для корректной работы всех ее узлов. В многопроцессорных системах важнейшими компонентами являются процессорные элементы (процессор + память) и коммуникационная сеть, соединяющая процессорные элементы и крэйты [1]. В данной работе рассматриваются высокопроизводительный интерфейс RapidIO (RIO) и способы инициализации такой среды.

Коммуникационная среда RIO состоит из коммутаторов и оконечных устройств (ОУ) [2]. Спецификацией определены два физических уровня: LP-LVDS – канал точка-точка, представляющий собой параллельный 8- и 16-разрядный дуплексный интерфейс с максимальной частотой тактового сигнала 1000 МГц, и LP-Serial – канал точка-точка, представляющий собой последовательный дуплексный интерфейс, состоящий из 1, 2, 4, 8 или 16 подканалов с максимальной скоростью передачи битового потока по каждому подканалу 10,3125 Гбод [3, 4].

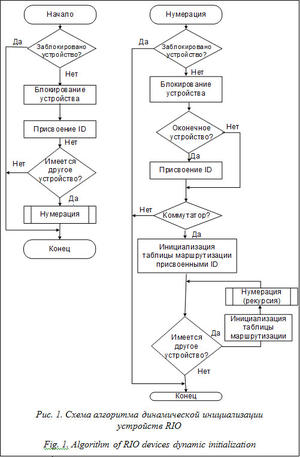

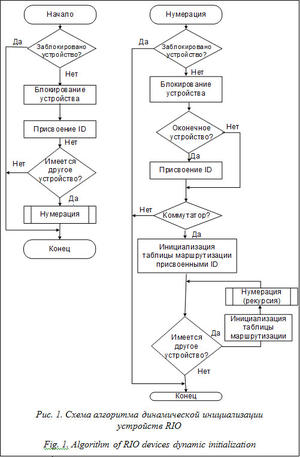

Инициализация коммуникационной среды RIO включает в себя назначение ОУ идентификаторов (8 или 16 бит) и прописывание коммутаторов маршрутами, определяющими пути пакетов от ОУ к ОУ [5]. Выделяют два подхода к инициализации коммуникационной среды – динамический и статический. Пример динамического подхода спецификации RIO [6] показан на рисунке 1.

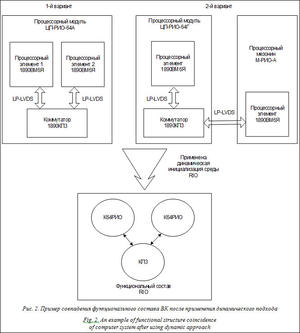

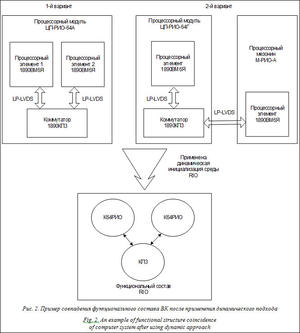

На практике приведенный алгоритм необходимо модифицировать прокладкой перекрестных маршрутов между всеми процессорными элементами (ПЭ) и ограничениями на просмотр портов коммутаторов (отдельные крэйты в сложной системе могут включаться неодновременно) – необходима локализация алгоритма в крэйте или в группе крэйтов. Кроме того, совершенно не учитываются предполагаемые потоки данных между ПЭ. Данный подход не подходит и для случая, когда требуется знание физической конфигурации вычислительного комплекса (ВК) после инициализации. В этом подходе при изменении физического состава ВК функциональный состав может остаться прежним. На примере процессорных модулей ЦП-РИО-64 и мезонина М-РИО-А, разработанных в НИИСИ РАН (рис. 2), показан результат определения устройств RIO. Процессорный модуль ЦП-РИО-64А включает в себя два процессора 1890ВМ6Я (устройство К64РИО) и коммута- тор 1890КП3Я (устройство КП3) [7], а модуль ЦП-РИО-64Г – один процессор 1890ВМ6Я и коммутатор 1890КП3Я. Мезонин М-РИО-А включает только процессор 1890ВМ6Я. И, если подключить М-РИО к модулю ЦП-РИО-64Г, полученный функциональный состав ВК после применения алгоритма обхода среды RIO будет совпадать, как и для модуля ЦП-РИО-64А.

На практике приведенный алгоритм необходимо модифицировать прокладкой перекрестных маршрутов между всеми процессорными элементами (ПЭ) и ограничениями на просмотр портов коммутаторов (отдельные крэйты в сложной системе могут включаться неодновременно) – необходима локализация алгоритма в крэйте или в группе крэйтов. Кроме того, совершенно не учитываются предполагаемые потоки данных между ПЭ. Данный подход не подходит и для случая, когда требуется знание физической конфигурации вычислительного комплекса (ВК) после инициализации. В этом подходе при изменении физического состава ВК функциональный состав может остаться прежним. На примере процессорных модулей ЦП-РИО-64 и мезонина М-РИО-А, разработанных в НИИСИ РАН (рис. 2), показан результат определения устройств RIO. Процессорный модуль ЦП-РИО-64А включает в себя два процессора 1890ВМ6Я (устройство К64РИО) и коммута- тор 1890КП3Я (устройство КП3) [7], а модуль ЦП-РИО-64Г – один процессор 1890ВМ6Я и коммутатор 1890КП3Я. Мезонин М-РИО-А включает только процессор 1890ВМ6Я. И, если подключить М-РИО к модулю ЦП-РИО-64Г, полученный функциональный состав ВК после применения алгоритма обхода среды RIO будет совпадать, как и для модуля ЦП-РИО-64А.

С данной задачей позволяет справиться статический подход. Он реализуется по заранее составленному набору служебных операций записи MAINTENANCE WRITE [8], которыми осуществляется инициализация устройств RIO в системе. Сложность этого подхода растет с количеством используемых устройств RIO.

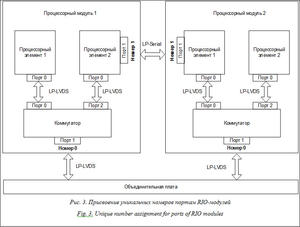

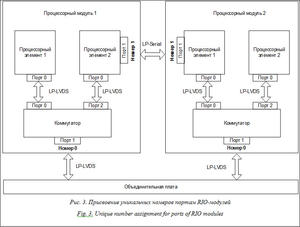

Для более эффективного составления набора операций MAINTENANCE WRITE предлагается использовать конфигуратор на основе базовых блоков RIO, которые представляют собой модели используемых модулей. Каждый модуль имеет порты RIO для связи с другими модулями, причем номера портов могут совпадать. Для описания модуля каждому порту присваивается уникальный номер, не зависящий от физического номера порта коммутатора (указанного в документации на микросхему), чтобы исключить пересечение номеров портов в модели (рис. 3). Каждый модуль уже имеет определенный состав устройств RIO, поэтому программно описать состав модуля и таблицу маршрутизации обмена в рамках модуля не составляет труда. Полученные базовые блоки подключаются между собой, используя географический адрес, уникальные номера портов и тип связей (например, объединительная плата или кабель). В итоге конфигуратору на вход поступают структуры вида: {географический адрес, модель, соединения}. Например: {ГА_N, Модель_N, {Тип связи, порт_ГА_N, ГА_K, порт_ГА_K}}, где K и N – любые два модуля.

Для более эффективного составления набора операций MAINTENANCE WRITE предлагается использовать конфигуратор на основе базовых блоков RIO, которые представляют собой модели используемых модулей. Каждый модуль имеет порты RIO для связи с другими модулями, причем номера портов могут совпадать. Для описания модуля каждому порту присваивается уникальный номер, не зависящий от физического номера порта коммутатора (указанного в документации на микросхему), чтобы исключить пересечение номеров портов в модели (рис. 3). Каждый модуль уже имеет определенный состав устройств RIO, поэтому программно описать состав модуля и таблицу маршрутизации обмена в рамках модуля не составляет труда. Полученные базовые блоки подключаются между собой, используя географический адрес, уникальные номера портов и тип связей (например, объединительная плата или кабель). В итоге конфигуратору на вход поступают структуры вида: {географический адрес, модель, соединения}. Например: {ГА_N, Модель_N, {Тип связи, порт_ГА_N, ГА_K, порт_ГА_K}}, где K и N – любые два модуля.

По этим данным формируется набор служебных пакетов записи MAINTENANCE WRITE. Так как каждый ВК в основном содержит в себе набор однотипных модулей, связи между оконечными устройствами внутри модуля в ВК повторяются. При использовании базовых блоков модуля в несколько раз сокращается время, которое требуется на описание повторяющихся связей между устройствами RIO, в зависимости от используемых модулей в ВК. Полученная инициализация позволяет провести проверку соответствия ВК с заявленной схемой подключения прибора.

По этим данным формируется набор служебных пакетов записи MAINTENANCE WRITE. Так как каждый ВК в основном содержит в себе набор однотипных модулей, связи между оконечными устройствами внутри модуля в ВК повторяются. При использовании базовых блоков модуля в несколько раз сокращается время, которое требуется на описание повторяющихся связей между устройствами RIO, в зависимости от используемых модулей в ВК. Полученная инициализация позволяет провести проверку соответствия ВК с заявленной схемой подключения прибора.

В случае, если полученная инициализация RIO для тестирования многопроцессорной системы используется многократно, можно воспользоваться аппаратной поддержкой инициализации таблицы маршрутизации RIO, встраиваемой в коммутаторы. Принцип работы следующий: к коммутатору подключается EEPROM по интерфейсу I2C, в него прописываются (по определенному формату) адреса регистров и их значения, после включения питания производится выгрузка этих значений в регистры коммутатора RIO. В результате настраиваются таблицы маршрутизации этих коммутаторов при загрузке системы и сокращается время на программную инициализацию среды. Данный подход реализован в коммутаторах 1890КП3Я (микросхема) НИИСИ РАН и в коммутаторах компании Integrated Device Technology (IDT) [9].

Динамический подход применяется на этапе отладки многопроцессорных систем и в тестовых задачах. Предлагаемый способ инициализации среды RIO хорошо применим к тестируемой системе [10]. Эффективность данного способа в большей мере проявляется при построении различных модификаций многопроцессорной системы на базе подготовленных базовых блоков RIO.

Литература

1. Бобков С.Г., Косарев И.М. Методы повышения производительности вычислительных систем // Прилож. к журн. «Информационные технологии». 2012. № 10. 32 с.

2. Fuller S. RapidIO. The Embedded Systems Interconnect. John Wiley & Sons, Ltd, 2005.

3. RapidIO Interconnect Specification. Part 4: Physical Layer 8/16 LP-LVDS Specification. Revision 3.0. RapidIO Trade Asso- ciation, 2013. URL: http://www.rapidio.org/specs/current/2013-oct23.zip (дата обращения: 16.01.2014).

4. RapidIO Interconnect Specification. Part 6: LP-Serial Physical Layer Specification. Revision 3.0. RapidIO Trade Association, 2013. URL: http://www.rapidio.org/specs/current/2013-oct23.zip (дата обращения: 16.01.2014).

5. Бакулин А.А. Проверка допустимости схемы маршрутизации в системе RapidIO // Программные продукты и системы. 2011. № 4. С. 20–23.

6. RapidIO Interconnect Specification. Annex 1: Software/ System Bring Up Specification. Revision 3.0. RapidIO Trade Association, 2013. URL: http://www.rapidio.org/specs/current/2013-oct23.zip (дата обращения: 16.01.2014).

7. Сердин О.В., Бобков С.Г., Кондратьева Н.В., Ере- мин А.А. Разработка высоконадежных многопроцессорных модулей на базе высокоскоростных каналов rapidio // Программные продукты и системы. 2013. № 4. С. 49–55.

8. RapidIO Interconnect Specification. Part 1: Input/Output Logical Specification. Revision 3.0. RapidIO Trade Association, 2013. URL: http://www.rapidio.org/specs/current/2013-oct23.zip (дата обращения: 16.01.2014).

9. IDT. URL: www.idt.com/document/man/tsi578-user-manual (дата обращения: 26.09.2014).

10. Лавринов Г.А. Способы повышения эффективности отладки и тестирования многопроцессорных систем // Программные продукты и системы. 2012. № 3. С. 86–89.

References

1. Bobkov S.G., Kosarev I.M. Methods of computer systems performance increasing. Informatsionnye tekhnologii

[Information technologies]. 2012, no. 10, pp. 1–32 (in Russ.).

2. Fuller S. RapidIO. The Embedded Systems Interconnect. John Wiley & Sons Publ., Ltd, 2005.

3. RapidIO Interconnect Specification. P. 4: Physical Layer 8/16 LP -LVDS Specification. Revision 3.0. RapidIO Trade

Association, 2013, available at: http://www.rapidio.org/specs/current/2013-oct23.zip (accessed January 16, 2014).

4. RapidIO Interconnect Specification. P. 6: LP-Serial Physical Layer Specification. Revision 3.0. RapidIO Trade

Association, 2013, available at: http://www.rapidio.org/specs/current/2013-oct23.zip (accessed January 16, 2014).

5. Bakulin A.A. Validation of routing scheme in rapidio system. Programmnye produkty i sistemy [Software &

Systems]. 2011, no. 4, pp. 20–23 (in Russ.).

6. RapidIO Interconnect Specification. Annex 1: Software/System Bring Up Specification. Revision 3.0. RapidIO Trade

Association, 2013, available at: http://www.rapidio.org/specs/current/2013 -oct23.zip (accessed January 16, 2014).

7. Serdin O.V., Bobkov S.G., Kondrateva N.V., Eremin A.A. Design of high reliability multiprocessor modules based

on high-performance rapidio interconnect architecture. Programmnye produkty i sistemy [Software & Systems]. 2013, no. 4,

pp. 49–55 (in Russ.).

8. RapidIO Interconnect Specification. P. 1: Input/Output Logical Specification. Revision 3.0. RapidIO Trade

Association, 2013, available at: http://www.rapidio.org/specs/current/2013-oct23.zip (accessed January 16, 2014).

9. IDT, available at: www.idt.com/document/man/tsi578-user-manual (accessed September 26, 2014).

10. Lavrinov G.A. Methods of efficiency increasing of debugging and testing for multiprocessor systems. Programmnye

produkty i sistemy [Software & Systems]. 2012, no. 3, pp. 86–89 (in Russ.).